- 您现在的位置:买卖IC网 > Sheet目录3832 > AT87C52X2-3CSUM (Atmel)IC 8051 MCU 8K OTP 40MHZ 40DIP

22

TS8xCx2X2

4184I–8051–02/08

Interrupt System

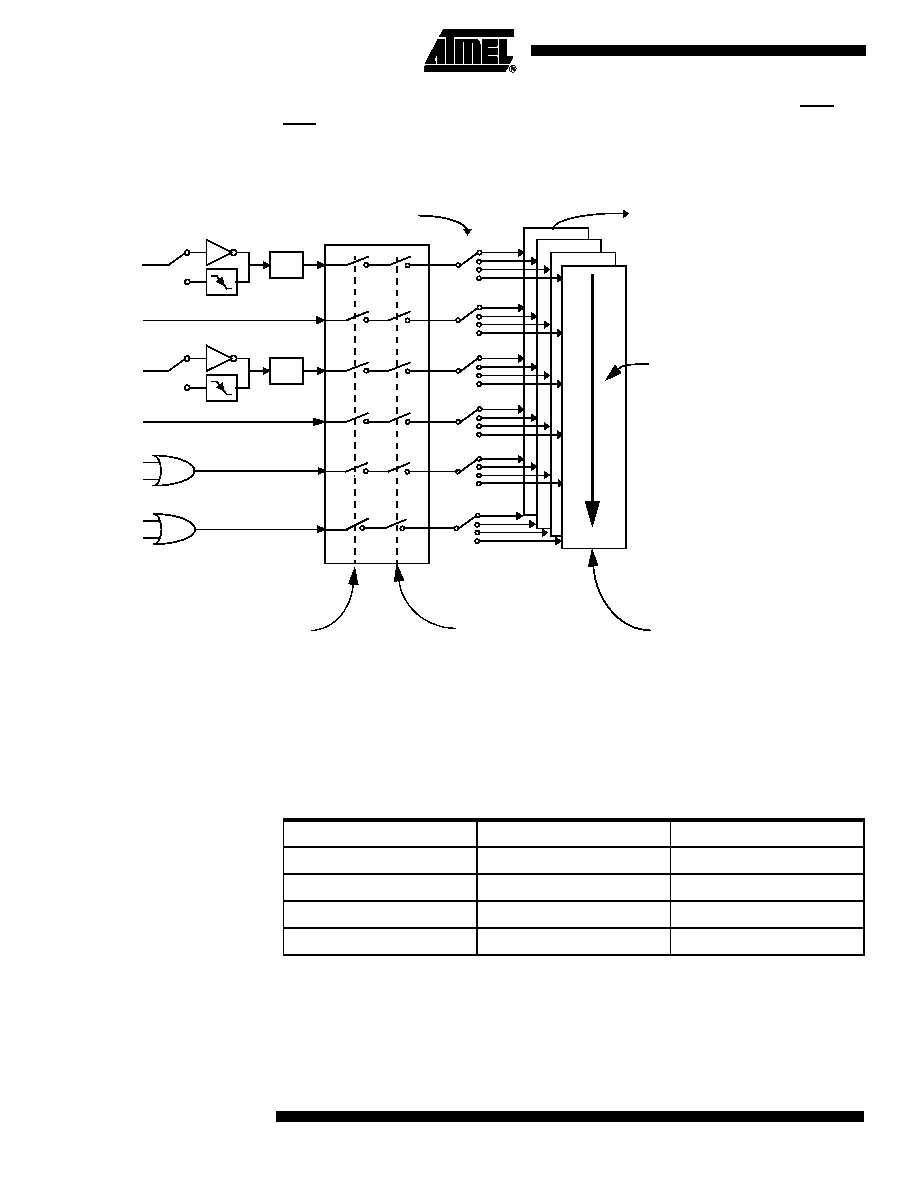

The TS80C52X2 has a total of 6 interrupt vectors: two external interrupts (INT0 and

INT1), three timer interrupts (timers 0, 1 and 2) and the serial port interrupt. These inter-

rupts are shown in Figure 9.

Figure 9. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clear-

ing a bit in the Interrupt Enable register (See Table 12.). This register also contains a

global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority lev-

els by setting or clearing a bit in the Interrupt Priority register (See Table 13.) and in the

Interrupt Priority High register (See Table 14.). shows the bit values and priority levels

associated with each combination.

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another

low-priority interrupt. A high-priority interrupt can’t be interrupted by any other interrupt

source.

If two interrupt requests of different priority levels are received simultaneously, the

request of higher priority level is serviced. If interrupt requests of the same priority level

IE1

0

3

High priority

interrupt

Interrupt

polling

sequence, decreasing from

high to low priority

Low priority

interrupt

Global Disable

Individual Enable

EXF2

TF2

TI

RI

TF0

INT0

INT1

TF1

IPH, IP

IE0

0

3

0

3

0

3

0

3

0

3

Table 11. Priority Level Bit Values

IPH.x

IP.x

Interrupt Level Priority

0

0 (Lowest)

0

1

0

2

1

3 (Highest)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C924-04/L

IC MCU OTP 4KX14 LCD DVR 68PLCC

PIC16F767-I/SO

IC PIC MCU FLASH 8KX14 28SOIC

PIC24FJ64GA310-I/PF

MCU 16BIT 64KB FLASH 100TQFP

DSPIC33FJ64GP202-E/MM

IC DSPIC MCU/DSP 64K 28-QFN

PIC16F876A-I/ML

IC MCU FLASH 8KX14 A/D 28QFN

PIC16F876A-I/SO

IC MCU FLASH 8KX14 EE 28SOIC

PIC16F876A-I/SP

IC MCU FLASH 8KX14 EE 28DIP

AT87C51RD2-3CSUM

IC 8051 MCU 64K OTP 40MHZ 40DIP

相关代理商/技术参数

AT87C52X2-3CSUV

功能描述:8位微控制器 -MCU Microcontroller

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLRUM

功能描述:8位微控制器 -MCU 0.5um RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUL

功能描述:8位微控制器 -MCU C72X2C52 0.5m OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUM

功能描述:8位微控制器 -MCU C72X2 C52 0.5 m X 2 OTP 0.5 NV RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller 8 Kbytes ROM/OTP, ROMless

AT87C52X2-SLRUL

功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-SLRUM

功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-SLSUL

功能描述:8位微控制器 -MCU OTP C52/8K 40MHZ 3V COM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT